인텔® 아톰™ 프로세서 C2000 제품군(이전 명칭 Rangeley)

☞ 개요

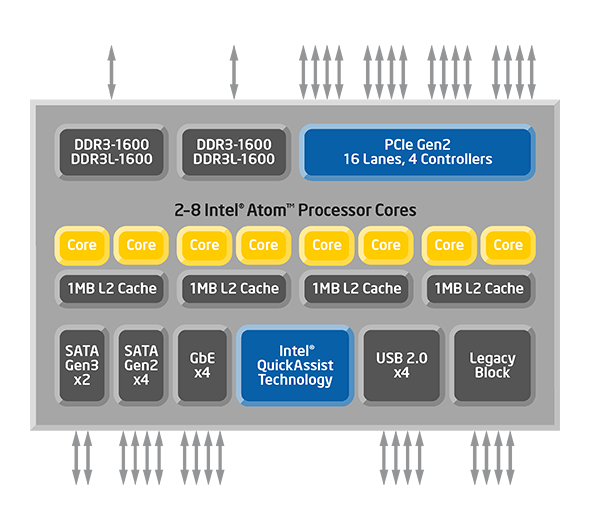

Based on the low-power Silvermont microarchitecture, this product family extends the scalability of Intel® architecture into smaller footprint and dense communications and intelligent systems. This product family offers a range of multi-core processing capabilities (from two cores to eight cores) and features high levels of I/O and acceleration integration, resulting in a scalable, single-chip system-on-chip (SoC).

• Based on the 22-nanometer process technology with 3-D tri-gate transistors, the product family provides optimal performance per watt, addressing the needs of thermally constrained solutions, such as entry to midrange branch office routers, security appliances, network access, communications servers, small cells, control plane processing, and storage.

• Pin-to-pin compatible, this product family allows developers to scale platforms seamlessly with design reuse. A range of thermal design power (TDP) from 7 watts to 20 watts supports energy-efficient network designs, including fanless embedded designs.

• When paired with the Intel® Data Plane Development Kit (Intel® DPDK), this platform improves packet processing speeds to handle increased network traffic data rates and associated control and signaling infrastructure requirements.

Specifications| Product | Intel®

Atom™

Processor

C2758 | Intel®

Atom™

Processor

C2738 | Intel®

Atom™

Processor

C2718 | Intel®

Atom™

Processor

C2558 | Intel®

Atom™

Processor

C2538 | Intel®

Atom™

Processor

C2258 | Intel®

Atom™

Processor

C2358 | Intel®

Atom™

Processor

C2338 | | Cores | 8 | 8 | 8 | 4 | 4 | 4 | 2 | 2 | Core

Frequency | 2.4GHz | 2.4GHz | 2.0GHz | 2.4GHz | 2.4GHz | 1.7GHz | 1.7GHz | 1.7GHz | | TDP | 20W | 20W | 18W | 15W | 15W | 13W | 7W | 7W | Memory

Type | DDR3/3L | DDR3/3L | DDR3/3L | DDR3/3L | DDR3/3L | DDR3/3L | DDR3/3L | DDR3/3L | Memory

Frequency | 1600 | 1600 | 1333 | 1600 | 1600 | 1333 | 1333 | 1333 | Memory

Channels | 2 | 2 | 2 | 2 | 2 | 2 | 1 | 1 | PCIe Gen2

Lanes /

Controllers | 16 / 4 | 16 / 4 | 16 / 4 | 16 / 4 | 16 / 4 | 16 / 4 | 8 / 4 | 8 / 4 |

USB 2.0

Ports | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | SATA 2.0

ports | 4 | 4 | 4 | 4 | 4 | 4 | 2 | 4 | SATA 3.0

ports | 2 | 2 | 2 | 2 | 2 | 2 | 2 | 2 | | GbE ports | 4 | 4 | 4 | 4 | 4 | 4 | 2 | 4 | Intel®

QuickAssist

Technology | Yes | No | Yes | Yes | No | Yes | Yes | No |

☞ Rangeley SoC Series Features

The main SoC architectural features are:

• SKUs containing two, four, or eight cores (Table 1-2 on page 60)

— Intel® Xeon® processor Instruction Set Architecture (ISA) compatibility

— Out-of-order instruction execution

— Intel® Virtualization Technology, VT-x2

— 1 MB shared L2 Cache (per two cores), 4 MB L2 total for the eight-core SKU

— SKU base frequencies of 1.7 GHz and 2.4 GHz

— Intel® Turbo Boost Technology for speeds up to 2.7 GHz depending on SKU

• Dual-Channel DDR3 Memory

— Single- or Dual-Channel Memory Controller, SKU dependent

— DDR3L (1.35V), DDR3 (1.5V), SKU dependency

— SDRAM speeds up to 1600 MT/s depending on SKU

— ECC support

— Support for single- or dual-rank DIMMs

— Support for two DIMMs per channel

— Up to 64-GB DDR3 memory capacity support, depending on product SKU.

• Integrated

— PCI Express* Gen 2 Root Ports, up to 8 or 16 lanes depending on SKU, bifurcates to 4 controllers

— SoC

• Network Controller Sideband Interface (NC-SI) allows for connectivity to a Baseboard Management Controller (BMC) for the purpose of enabling out-of-band remote manageability.

• SMBus ports are available and continue to be available to enable network manageability implementations.

• SoC designs can use either SMBus or NC-SI for connectivity to the BMC, but not both.

• The SoC GbE Interface provides support for IEEE 802.3 1000BASE-KX and also introducing non-standard 2.5 GbE implementations.

— SATA2 x4 or X2, depending on SKU, to support high-capacity rotational media

— Two SATA3 Ports to support solid-state drives (SSDs) requiring high rates of I/O operations per second (IOPS)

— USB 2.0 x4, EHCI compliant

— SMBus x4 (Host, PECI, normal SPD, and LAN interface)

• Based on new Intel SoC design technology

— Next-Generation SoC System Agent (SSA)

— Significant improvements in performance and latency than current Intel® AtomTM processor system agents.

— Common legacy block controllers (SPI, UART, RTC, HPET, etc.)

• Power Management

— Significant improvements to support lightweight server power management

— Exposed PECI over SMBus mechanism

— Highly-optimized Power Management Unit (PMU)

— Support for Turbo, Running Average Power Limiting (RAPL)

— SVID support to optimize power consumption

• Server-Class Reliability, Availability and Serviceability (RAS)

— Data and address for memory ECC

— Demand and Patrol Scrub to detect and correct memory errors

— Significant internal data-path parity protection

• Enhanced cryptographic/content processing acceleration via integrated Intel®

QuickAssist Integrated Accelerator

— Bulk Encryption (AES, 3DES, RC4)

— Authentication (SHA1, MD5)

• Package parameters: 34 mm x 28 mm

• Ball Count: 1283

☞ Platform Brief: Intel® Atom™ Processor C2000 Product Family-Based Platforms for Communications Infrastructure

|

|